# Software Defined Data Plane For Deep Data Plane Programmability

## Aki Nakao Professor, The University of Tokyo Chairman, 5GMF Network Architecture Committee 2017/11/20

## Challenges in Data Plane Programmability

- Ease of programming

- Processing & forwarding performance

- Extending SDN Southbound / Actions

- SDN/NFV cross-layer optimization

- Cost

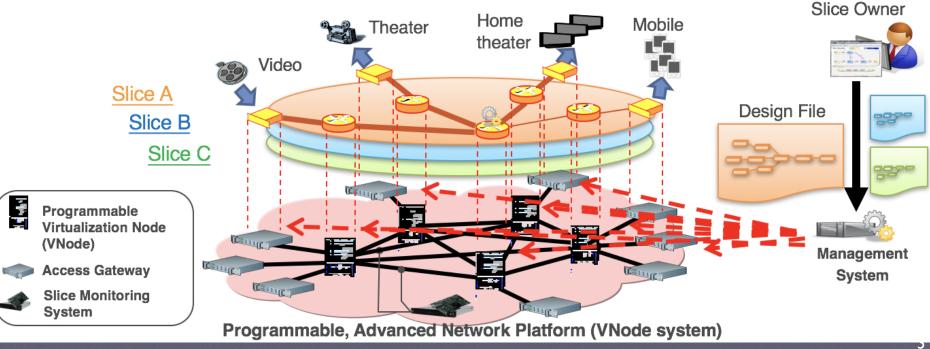

# Network virtualization platform

- Common SDN  $\geq$

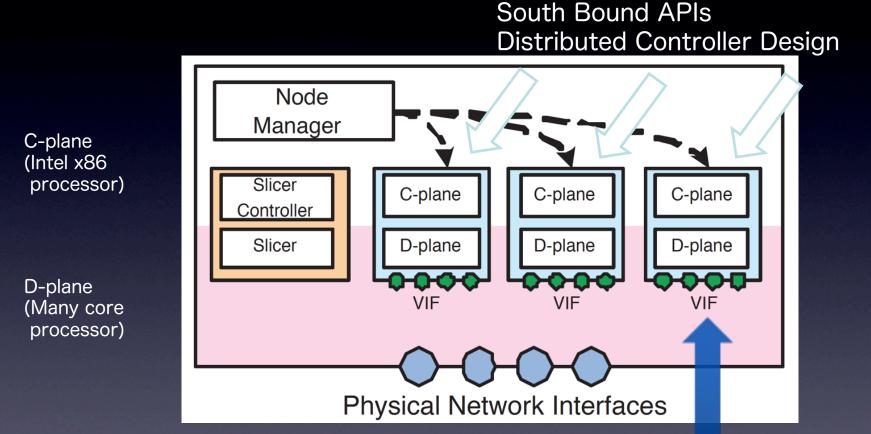

- Software based managing network with separating C-plane/D-plane

- Cutting OPEX/CAPEX by automation by software and Constructing NW by common HW

- Network virtualization platform  $\geq$

- Realizing "Deep programmability" by totally virtualization of networking and computing adding separating C/D-plane

- Realizing service chaining without limitation of physical network

@GEC21

Innovative B&D by N

## **Our Research Activities on Network Slicing**

US

Worldwide

NFV

2002- PlanetLab

2008 VNode Project Phase1 2008 GENI Kick Off (\$12M 29institutions) (NICT/Utokyo/NTT/NEC/ Hitachi/Fujitsu) 2009 GEC4 (Mar) GEC5(Jul) GEC6(Nov) 2010 GEC7 (Mar) GEC8(Jul) GEC9(Nov) 2011 Vnode /FLARE Project 2011 GEC10 (Mar) GEC11(Jul) GEC12(Nov) plenary Phase2 (Utokyo/NTT/NEC/ 2012 GEC13 (Mar) GEC14(Jul) GEC15(Nov) plenary Hitachi/Fujitsu/KDDI) 2013 GEC16 (Mar) GEC17(Jul) GEC18(Nov) **SDN** 2014 Vnode Project Completion 2014 GEC19 (Mar) GEC20(Jul) GEC21(Nov) **Best Demo** 2014 5G/IoT Slicing

## FLARE Board V1.3 (New)

#### 36 Core Sliceable Data Plane Board

# FLARE Node Architecture

Virtual Forwarding Context (VFC)

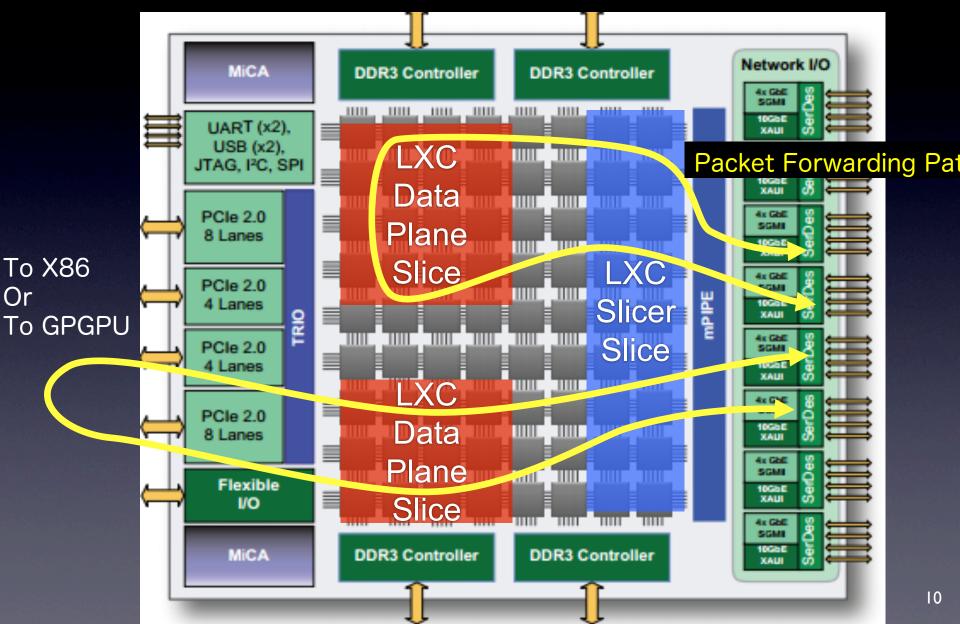

# Slice Architecture on NPU

LXC: Linux Container on Zero Overhead Linux (ZOL)

# FLARE D-plane H/W Platforms

- Many Core NPU

- Mellanox TileGX36

- Mellanox TileGX72

- Mellanox BlueField (Planned)

- Many Core CPU

- Intel x86 Only (DPDK)

- AMD Epyc/ Threadripper (On-Going)

- Reconfigurable ASIC

- Intel x86 + Cavium Thunder X (Planned)

- Intel x86 + Barefoot/P4 (Planned)

All Rights Reserved by Akihiro Nakao, 2017

Programmability High Performance Scalability Low Power

High Performance (Frequency) Programmability

High Performance

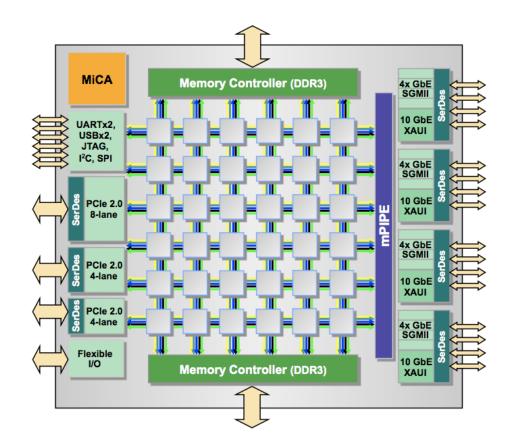

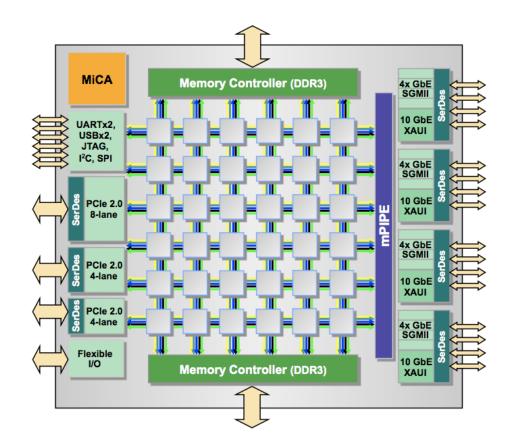

# TILE-Gx36<sup>™</sup>: Scaling to a broad range of applications

- 36 Processor Cores

- 866M, 1.2GHz, 1.5GHz clk

- 12 MBytes total cache

- 40 Gbps total packet I/O

- 4 ports 10GbE (XAUI)

- 16 ports 1GbE (SGMII)

- 48 Gbps PCIe I/O

- 2 16Gbps Stream IO ports

- Wire-speed packet engine

- 60Mpps

- MiCA engine:

- 20 Gbps crypto

- Compress & decompress

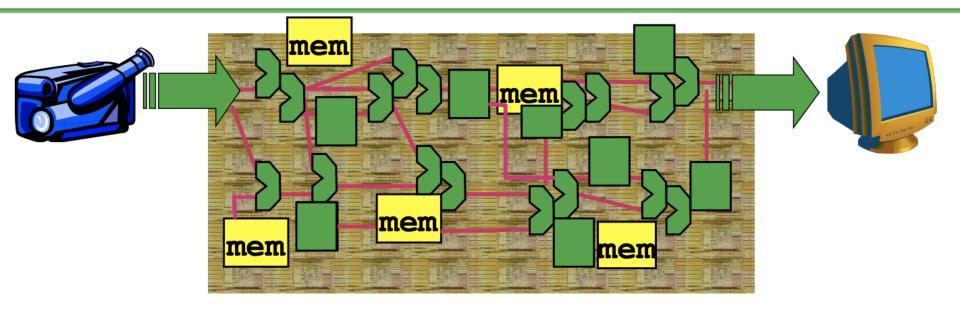

# **Take Inspiration from ASICs**

ASICs have high performance and low power

- Custom-routed, short wires

- Lots of ALUs, registers, memories huge on-chip parallelism

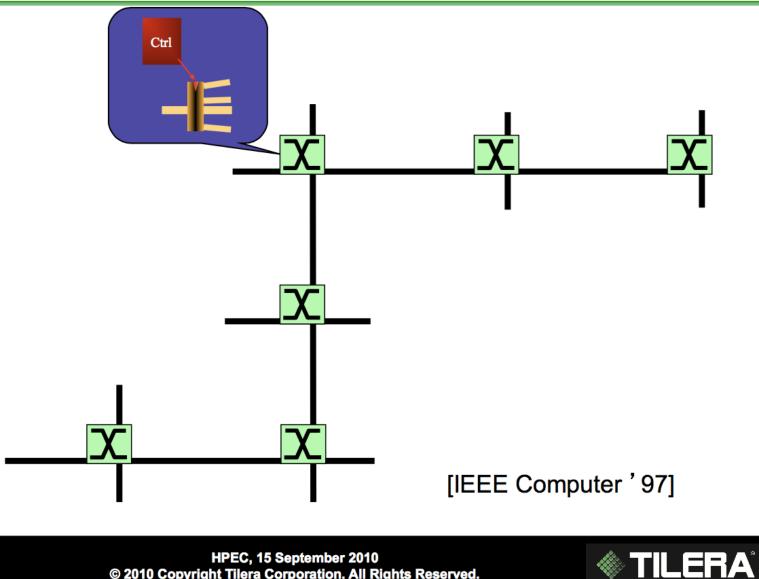

# But how to build a programmable chip?

HPEC, 15 September 2010 © 2010 Copyright Tilera Corporation. All Rights Reserved.

# **Replace Long Wires with Routed** Interconnect

© 2010 Copyright Tilera Corporation. All Rights Reserved.

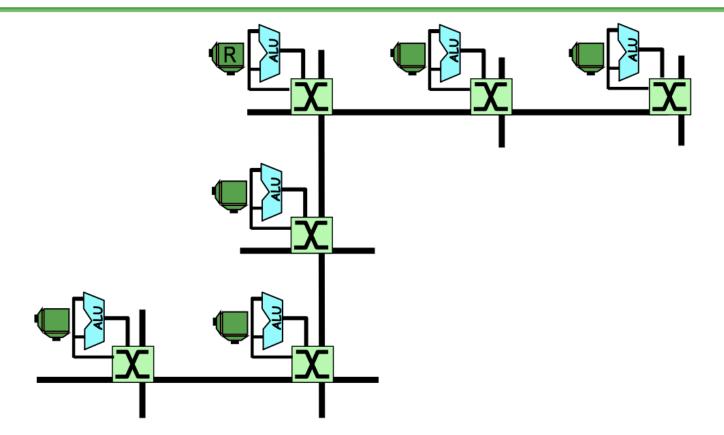

# ... To Distributed ALUs, Routed Bypass Network

#### Scalar Operand Network (SON) [TPDS 2005]

HPEC, 15 September 2010 © 2010 Copyright Tilera Corporation. All Rights Reserved.

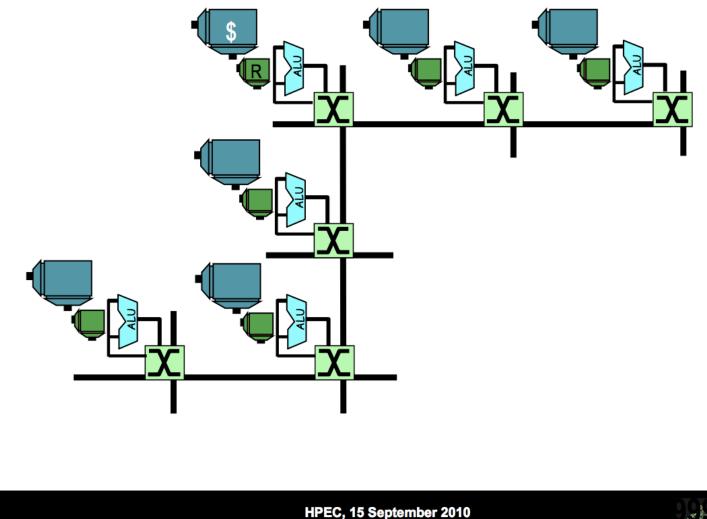

# ...to a Distributed Shared Cache

© 2010 Copyright Tilera Corporation. All Rights Reserved.

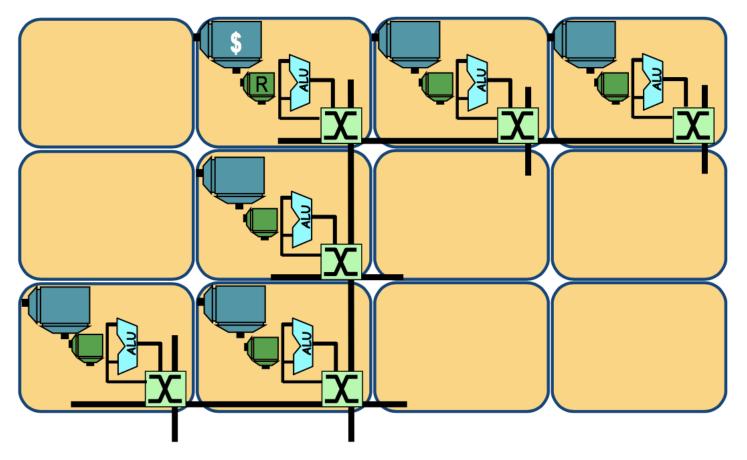

# Distributed Everything + Routed Interconnect → Tiled Multicore

#### Each tile is a processor, so programmable

HPEC, 15 September 2010 © 2010 Copyright Tilera Corporation. All Rights Reserved.

# TILE-Gx36<sup>™</sup>: Scaling to a broad range of applications

- 36 Processor Cores

- 866M, 1.2GHz, 1.5GHz clk

- 12 MBytes total cache

- 40 Gbps total packet I/O

- 4 ports 10GbE (XAUI)

- 16 ports 1GbE (SGMII)

- 48 Gbps PCIe I/O

- 2 16Gbps Stream IO ports

- Wire-speed packet engine

- 60Mpps

- MiCA engine:

- 20 Gbps crypto

- Compress & decompress

Seeking viable applications of Software Defined Data Plane…

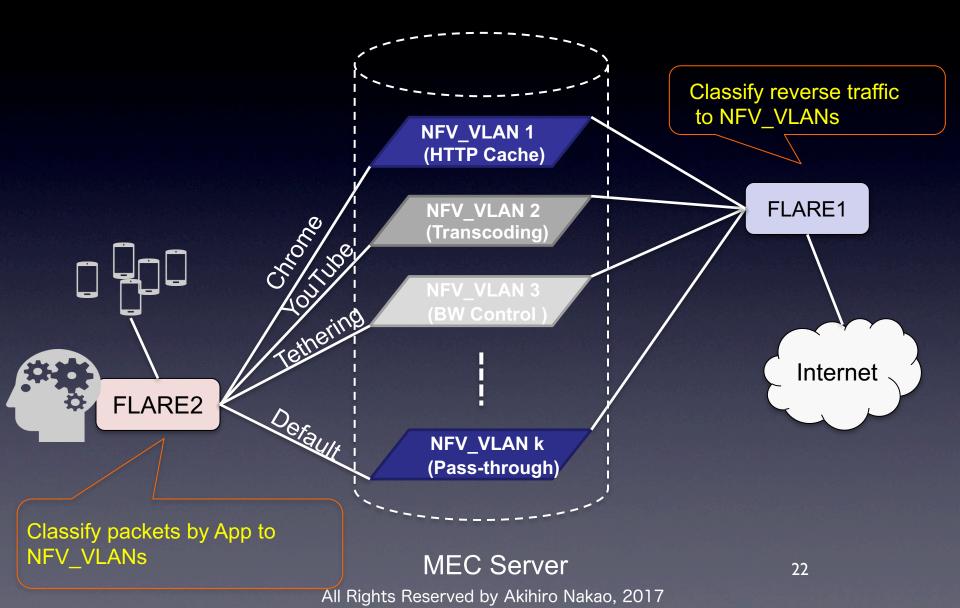

## **Application-Specific MEC Processing**

# **Application Identification**

Remote console of programmable network node (FLARE)

Smartphone connected to our MVNO

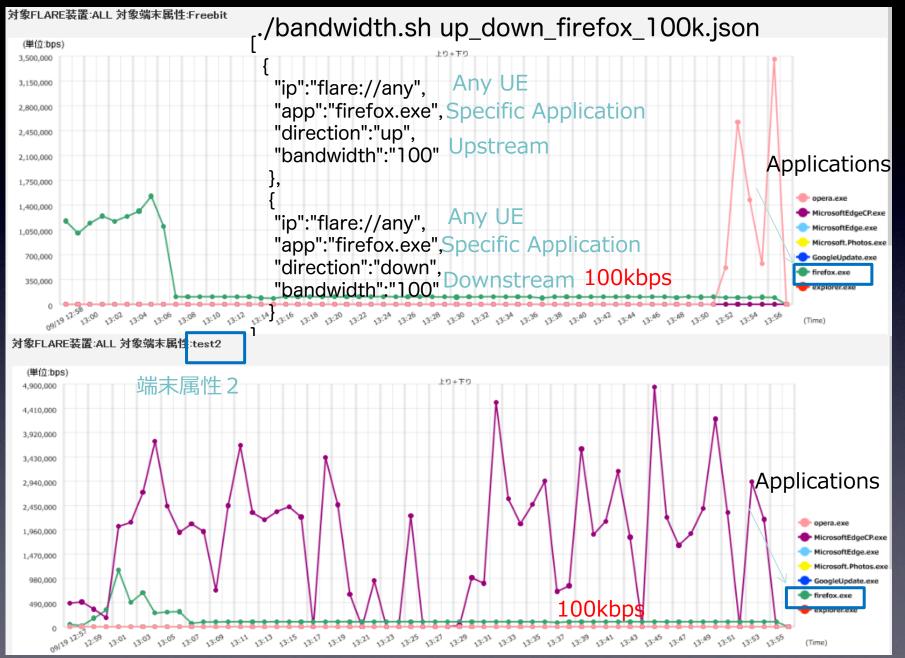

# **Per Application Slicing**

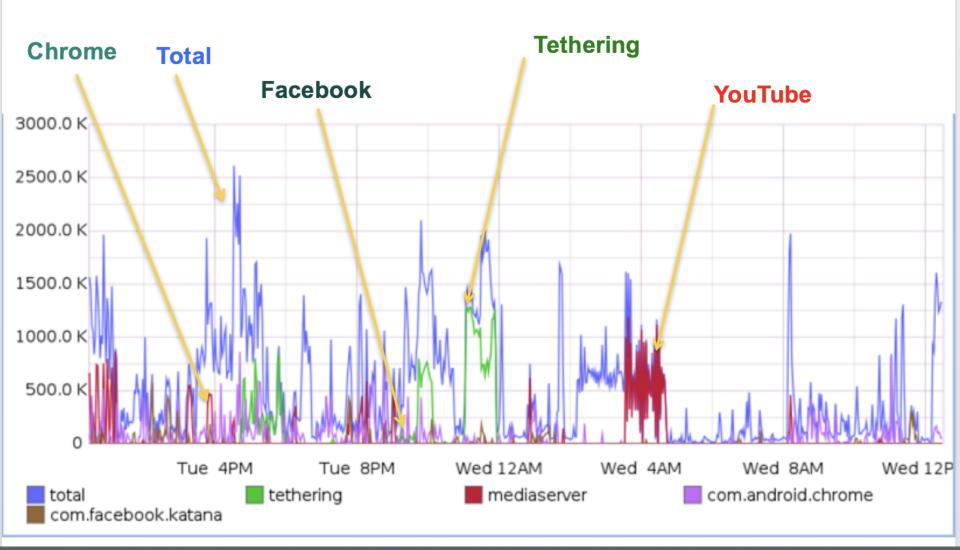

## **Application Specific Traffic Breakdown**

### Per-Applicaons QoS

#### Collaboration with Kenjiro@IIJ

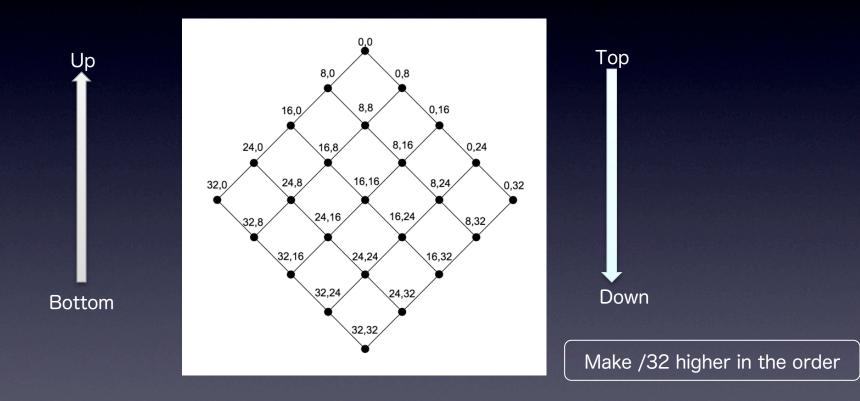

## Anomaly Detection algorithm→ Hierarchical Heavy Hitters Revisited

Prefix-length-sum as aggregation order

## Challenges in Data Plane Programmability

- Ease of programming

- Processing & forwarding performance

- Extending SDN Southbound / Actions

- SDN/NFV cross-layer optimization

- Cost

## And "viable" applications...